Open-source ASIC solver for the van der Pol nonlinear oscillator using 16-bit posits submitted to TinyTapeout 7.

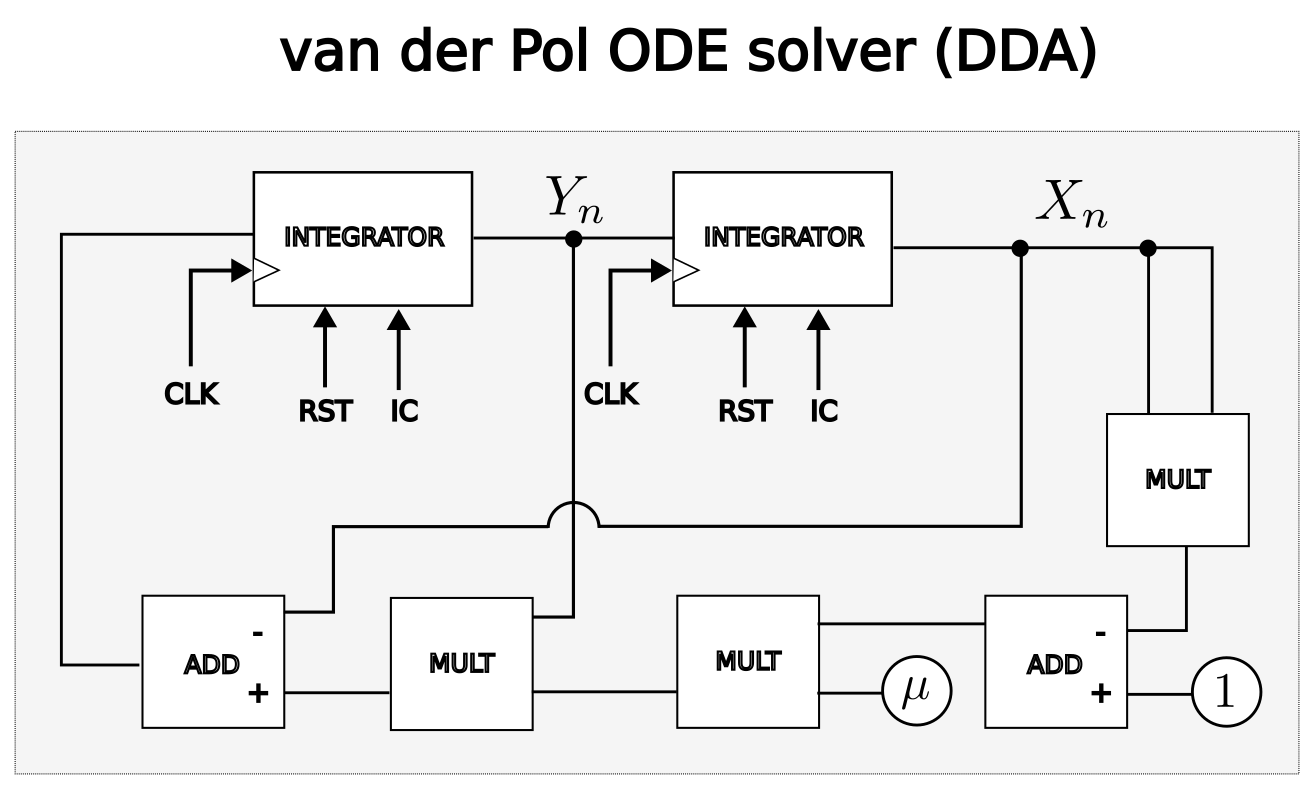

A Digital Differential Analyzer (DDA) is a digital circuit that uses integrators to solve differential equations in digital systems. This project implements an Euler integration algorithm in hardware using an alternative to the IEEE-754 floating point numerical system called Posit (see below). To program a DDA one has to wire basic components such as adders, multipliers and integrators together to express the desired set of equations that describes the dynamical system, in a similar fashion as the old analog computers were programmed.

The van der Pol oscillator is decribed by the second order nonlinear ordinary differential equation (ODE) given by

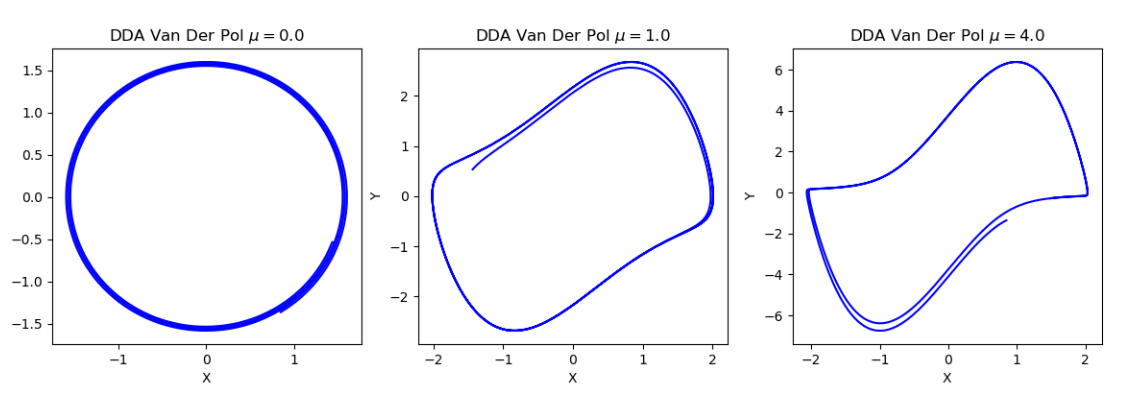

The phase portraits for varying parameter

The set of coupled ODEs can be implemented in digital circuit as shown in the diagram below. At each DDA clock the integrators calculate the solutions for one time step

For simplicity and limited chip area the time step is fixed by

Posit number offers a new way to encode and operate with floating point numbers in digital systems that is gaining attention for its applications in AI hardware accelerators. Compared to the standard IEEE-754 floating-point format, posits offer a few advantages including the ability to trade off between precision and dynamic range for a given number of bits allowing hardware optimizations to specific applications.

For numerical applications, the IEEE-754 has many drawbacks that can produce inconsistencies and wrong results.

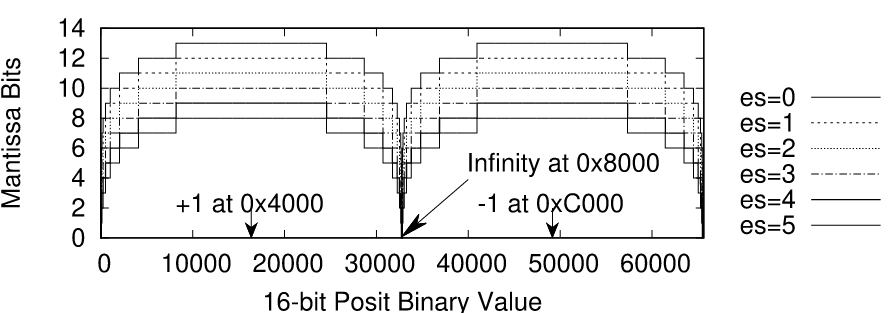

A posit format is defined by the combinations of its word size (N) and exponent size (es) as a tuple (N,es). In this project posits (16,1) were used, meaning 16-bit word and 1-bit exponent sizes. Different choices of ES is possible leading to distinct dynamic ranges and precisions.

The composition of a posit enconding is shown in the figure below. It consists of:

- Sign bit (s): 0 for positive and 1 for negative

- Regime bits (r): sequences of either all 0 or 1, terminated by an opposite bit. Its value is determined by its run-length. For instance, a sequence of m bits 0 terminated by 1 defines negative regime-bit value of k = -m , e.g. (0001 -> -3). For a sequence of m bits 1 terminated by a bit 0 the positive regime-bit value is defined by k = m-1, .e.g (1110 -> k = 2).

- Exponent bits (e): unsigned integer which can be maximum of ES bits in lenght.

- Fraction bits (f): any remaining bits after the regime and exponent bits (if any) define the fraction 1.f as in a float number (there are no subnormals in posits). The maximum fraction bits width is N-es-3.

Dynamic range is usually measured in decades and it is defined by the logarithm base 10 of the ratio between the largest and the smallest representable numbers. The largest posit number, called maxpos, occurs when k is as large as possible, when all the bits after the sign bit are 1s (k = N-2) and is given by

The smallest posit number, minpos is obtained when k is as negative as possibl and is given by

And the expression for the dynamic range is

The precision is related to the width of the fraction bits used and varies with es. The figure below shows the width of fraction bits (matissa) for 16-bit posits with different values of es. In general, posit representations have more fraction bits around